The objective of this project is to develop a reconfigurable verification environment that supports multiple protocols using the UVM methodology.

The first step will be to study and analyze the existing verification environment in order to see how it’s structured and to identify what components will have to be replaced. Then, with basis on that study, it will be proposed and discussed possible modifications to be applied to the studied system. After the discussion, the chosen approach will be implemented in the environment. Finally, to prove it’s working, the envinroment will verify a platform yet to be defined.

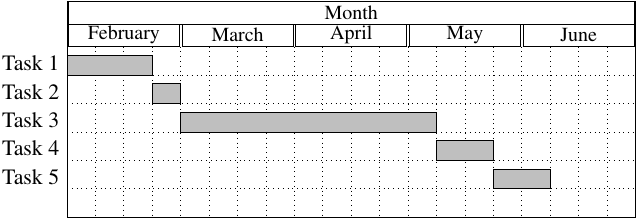

The distribution of the work throughout the semester is described on the following table:

| Task | Description | Start | Finish |

|---|---|---|---|

| Task 1 | Study of the existing UVM environment | 3 Feb | 21 Feb |

| Task 2 | Proposal of possible implementations | 24 Feb | 28 Feb |

| Task 3 | Implementation | 3 Mar | 2 May |

| Task 4 | Aplication of the researched solution to an existing platform | 5 May | 16 May |

| Task 5 | Writing of the dissertation | 19 May | 6 June |

The following figure represents the Gantt chart of the work plan:

The project will be realized in the offices of Synopsys Porto using the company’s resources. It’s foreseen the usage of the tools:

- VCS: Verilog Compiled code Simulator – Synopsys’ HDL compiler and simulator. Verilog and SystemVerilog code will be compiled with this tool.

- DVE: Discovery Visualization Environment – It’s an advanced debugger and waveform visualization environment from Synopsys. This tool will be used to debug the developed environments.

- UVM Reference Implementation. The UVM API that is freely available at Accellera’s website: http://www.accellera.org/downloads/standards/uvm

The following references are going to be consulted for this project:

- Book “SystemVerilog for Verification: A Guide to Learning the TestBench Language Features“, by Chris Spear

- Book “Comprehensive Functional Verification: The Complete Industry Cycle“, by John Goss